# INTRODUCTION TO MECHATRONIC DESIGN

# J. EDWARD CARRYER R. MATTHEW OHLINE THOMAS W. KENNY

Mechanical Engineering Stanford University

### **Prentice Hall**

Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montreal Toronto Delhi Mexico City Sao Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo

Vice President and Editorial Director, ECS: Marcia J. Horton Senior Editor: Tacy Quinn Acquisitions Editor: Norrin Dias Editorial Assistant: Coleen McDonald Vice President, Production: Vince O'Brien Senior Managing Editor: Scott Disanno Production Liaison: Jane Bonnell Production Editor: Pavithra Jayapaul, TexTech International Senior Operations Supervisor: Alan Fischer Operations Specialist: Lisa McDowell Executive Marketing Manager: Tim Galligan Marketing Assistant: Mack Patterson Senior Art Director and Cover Designer: Kenny Beck Cover Image Somatuscan/Shutterstock Art Editor: Greg Dulles Media Editor: Daniel Sandin Composition/Full-Service Project Management: TexTech International

Company and product names mentioned herein are the trademarks or registered trademarks of their respective owners. See p. xxiii for additional trademark acknowledgments.

**Copyright © 2011 by Pearson Education, Inc., Upper Saddle River, New Jersey 07458.** All rights reserved. Manufactured in the United States of America. This publication is protected by Copyright and permissions should be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. To obtain permission(s) to use materials from this work, please submit a written request to Pearson Higher Education, Permissions Department, 1 Lake Street, Upper Saddle River, NJ 07458.

The author and publisher of this book have used their best efforts in preparing this book. These efforts include the development, research, and testing of the theories and programs to determine their effectiveness. The author and publisher make no warranty of any kind, expressed or implied, with regard to these programs or the documentation contained in this book. The author and publisher shall not be liable in any event for incidental or consequential damages in connection with, or arising out of, the furnishing, performance, or use of these programs.

Library of Congress Cataloging-in-Publication Data

Carryer, J. Edward.

Introduction to mechatronic design / J. Edward Carryer, R. Matthew Ohline, Thomas W. Kenny. p. cm.

Includes bibliographical references and index.

ISBN-13: 978-0-13-143356-4 (alk. paper)

ISBN-10: 0-13-143356-3

Mechatronics. I. Ohline, R. Matthew. II. Kenny, Thomas William. III. Title.

TJ163.12.C37 2010 621-dc22

2010033713

Prentice Hall is an imprint of

www.pearsonhighered.com

10 9 8 7 6 5 4 3 2 1

ISBN-13: 978-0-13-143356-4 ISBN-10: 0-13-143356-3 a low impedance path between power and ground and leads to what is known as **shoot-through current**. Recall that in bipolar implementations of a totem-pole output stage, a resistor was placed between the power supply and the sourcing (upper) transistor to limit the shoot-through current. This approach is not realistic for a power driver because of the high currents involved. The presence of a resistor in a power driver would introduce unacceptably large drops in the voltage supplied to the load at the output and dissipate power inside the driver whenever it was sourcing current.

The designers of bridge drivers handle the problem of shoot-through currents by independently controlling the upper and lower transistors and intentionally staggering the time when one is switched off and the other is switched on—that is, a **dead time** is introduced during each transition. This dead time, when neither the upper nor lower transistor is being activated, allows time for the transistor that is turning off to fully reach the off state before the other transistor is commanded to turn on. The introduction of a dead time at transitions allows for the elimination of shoot-through current at the expense of switching time.

#### 17.6.2 H-Bridge Specifications

For bridge drivers, the most relevant output specifications are for the amount of voltage and current that can be controlled, the voltage losses to be expected across the switching elements, and the timing of the switching operations. The input specifications are important as well, of course, but this discussion centers on the performance of the outputs. The electrical specifications (both output and input) for the L293B, a device with four 1 A half-bridges, are shown in Figure 17.17.

This device uses separate power supply pins for the logic supply  $(V_{SS})$  and the motor supply  $(V_S)$ . Notice that the motor supply voltage can be as high as 36 V, however, it can be no lower than the logic supply voltage. This sets a lower limit on the motor voltage of 4.5 V.

The output voltage to the load is specified in terms of the voltage drop that will occur across each switching element ( $V_{\text{CEsatH}}$  for the upper, or sourcing, transistor and  $V_{\text{CEsatL}}$  for the lower, or sinking, transistor). It is important to recognize that when the L293B is operated as an H-bridge, there will be one sourcing transistor **and** one sinking transistor in the switched current path.

Near the bottom of the data sheet excerpt, we find the timing specifications for the device. As is common with power drivers, the timing specifications are given in two parts. The **delay** time is the time between a change in the input and the corresponding change in the output. In addition, there is a specification for the 10–90% **rise time** and **fall time**. Notice that the turn-on delay time is longer than the turn-off delay time plus the fall time, revealing the use of dead time to control the shoot-through current.

#### 17.7 THERMAL DESIGN ISSUES

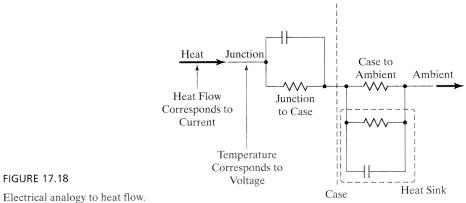

When switching substantial currents, the voltage losses that occur across the switching elements represent not only a loss in voltage to the load but also power ( $P = V \times I$ ) that must be dissipated within the power driver. This power is dissipated as heat in the chip, and it must be removed to keep the temperature from rising to a level that would cause damage to the driver. To facilitate the thermal analysis, manufacturers provide data to describe the thermal performance of the chips. The data provided are generally based on a simple heat flow model that has a direct analog in circuits (Figure 17.18).

In this model, the temperatures correspond to voltages and heat flows correspond to current flow. The resistors represent the resistance to heat flow ( $^{\circ}C/W$ ). The capacitors represent the thermal capacity of the case (and possibly a heat sink) and, when included, allow for the analysis of thermal transients. Basic thermal analysis is generally done at steady state, equivalent to DC, in which case the thermal capacitance terms are ignored.

i on a ridge,

L and is is a ers 23

is the they in the ons in duces

| Symbol           | Parameter                                | Test Condition                               | Min.            | Тур.     | Max.            | Unit |

|------------------|------------------------------------------|----------------------------------------------|-----------------|----------|-----------------|------|

| Vs               | Supply Voltage                           |                                              | V <sub>SS</sub> |          | 36              | V    |

| V <sub>SS</sub>  | Logic Supply Voltage                     |                                              | 4.5             |          | 36              | V    |

| l <sub>ŝ</sub>   | Total Quiescent Supply Current           | $V_i = L; I_o = 0; V_{inh} = H$              |                 | 2        | 6               | mA   |

|                  |                                          | $V_i = h; I_o = 0; V_{inh} = H$              |                 | 16       | 24              | mA   |

|                  |                                          | V <sub>inh</sub> = L                         |                 |          | 4               | mA   |

| I <sub>ss</sub>  | Total Quiescent Logic Supply<br>Current  | $V_i = L; I_o = 0; V_{inh} = H$              |                 | 44       | 60              | mA   |

|                  |                                          | $V_i = h$ ; $I_o = 0$ ; $V_{inh} = H$        |                 | 16       | 22              | mA   |

|                  |                                          | V <sub>inh</sub> = L                         |                 | 16       | 24              | mA   |

| ViL              | Input Low Voltage                        |                                              | -0.3            |          | 1.5             | V    |

| ViH              | Input High Voltage                       | $V_{SS} \le 7V$                              | 2.3             |          | Vss             | V    |

|                  |                                          | V <sub>SS</sub> > 7V                         | 2.3             |          | 7               | V    |

| liL              | Low Voltage Input Current                | V <sub>il</sub> = 1.5V                       |                 |          | -10             | μA   |

| liH              | High Voltage Input Current               | $2.3V \leq V_{1H} \leq V_{SS} - 0.6V$        |                 | 30       | 100             | μΑ   |

| VinhL            | Inhibit Low Voltage                      |                                              | -0.3            |          | 1.5             | V    |

| VinhH            | Inhibit High Voltage                     | V <sub>SS</sub> ≤7V                          | 2.3             |          | V <sub>ss</sub> | V    |

|                  |                                          | V <sub>SS</sub> > 7V                         | 2.3             | <b> </b> | 7               | V    |

| linhL            | Low Voltage Inhibit Current              | V <sub>inhL</sub> = 1.5V                     |                 | -30      | -100            | μΑ   |

| linnH            | High Voltage Inhibit Current             | 2.3V ≤V <sub>inhH</sub> ≤ Vss- 0.6V          |                 |          | ±10             | μA   |

| VCEsatH          | Source Output Saturation Voltage         | I <sub>o</sub> = -1A                         |                 | 1.4      | 1.8             | V    |

| VCEsatL          | Sink Output Saturation Voltage           | I <sub>o</sub> = 1A                          |                 | 1.2      | 1.8             | V    |

| VSENS            | Sensing Voltage (pins 4, 7, 14, 17) (**) |                                              |                 |          | 2               | V    |

| tr               | Rise Time                                | 0.1 to 0.9 V <sub>o</sub> (*)                |                 | 250      |                 | ns   |

| t <sub>f</sub>   | Fall Time                                | 0.9 to 0.1 V <sub>o</sub> (*)                |                 | 250      |                 | ns   |

| ton              | Turn-on Delay                            | 0.5 V <sub>i</sub> to 0.5 V <sub>o</sub> (*) |                 | 750      |                 | ns   |

| t <sub>off</sub> | Turn-off Delay                           | 0.5 V <sub>i</sub> to 0.5 V <sub>o</sub> (*) |                 | 200      |                 | ns   |

### **FIGURE 17.17**

The Electrical Specifications section for the L293B, a chip with four half-bridge drivers that can be combined to create two full H-bridges. (Copyright STMicroelectronics. Used with permission.)

FIGURE 17.18

| THERMAL DATA          |                                     |      |       |      |  |  |  |  |  |

|-----------------------|-------------------------------------|------|-------|------|--|--|--|--|--|

| Symbol                | Parameter                           |      | Value | Unit |  |  |  |  |  |

| Rth j-case            | Thermal Resistance Junction-case    | Max. | 14    | °C/W |  |  |  |  |  |

| R <sub>th</sub> j-amb | Thermal Resistance Junction-ambient | Max. | 80    | °C/W |  |  |  |  |  |

FIGURE 17.19

Thermal specifications for an L293B. (Copyright STMicroelectronics. Used with permission.)

To make this model more concrete, let's look at an example using the L293B. The thermal specifications for the L293B are shown in Figure 17.19.

We can use the junction-ambient specification to evaluate the thermal performance without an external heat sink or combine it with the specification for the junction-case to determine the case-ambient specifications for use in evaluating the system performance with a heat sink. Let's start our example with an application that does not use a heat sink.

The Absolute Maximum section of the data sheet states that the maximum allowable junction temperature is 150°C. If we want to analyze the worst-case power dissipation in steady state, we would use the maximum output current (1 A) and the maximum voltage drops across the switching elements (1.8 V for sourcing and 1.8 V for sinking, for a total of 3.6 V). This gives us a total power dissipation of approximately 3.6 W (we have ignored the power dissipated in the internal operation of the chip since it is much smaller than the power dissipated in the switching elements). Using the junction-ambient thermal resistance, we calculate the temperature rise across the case to be 3.6 W × 80°C/W = 288°C. If we limit the junction temperature to 150°C, as the data sheet tells us we must, we could not operate at an ambient temperature above -138°C. Clearly, this won't work! We have two choices as to how to proceed: we could ask "What current could we use and still keep the junction temperature low enough?"

If we wanted to operate at room temperature (25°C), we would be limited to a 125°C rise over ambient (ROA) temperature to meet the junction temperature limit. With a junction-ambient thermal resistance of 80°C/W, we would need to limit the power dissipation to  $125^{\circ}C/(80^{\circ}C/W) = 1.56$  W. Assuming worst-case voltage drops across the transistors that would limit the current to 1.56 W/3.6 V = 434 mA.

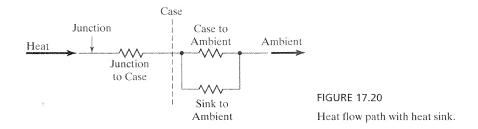

If 434 mA isn't enough for our application, we can consider adding a heat sink as an alternative. Given the specifications for the L293B, we can calculate the minimum thermal resistance for a heat sink that would allow us to dissipate the required power and meet the junction temperature limit. To determine this, we calculate the total thermal resistance needed to meet our maximum ROA:  $125^{\circ}$ C/3.6 W =  $34.7^{\circ}$ C/W. This total thermal resistance will be made up of the combination of the junction-case thermal resistance in series with the parallel combination of the case-ambient and sink-ambient thermal resistances (Figure 17.20). When using a heat sink, it is not uncommon (and produces a more conservative result) to ignore the case to ambient path.

mbined

## FIGURE 17.21 DIP heatsink.

To find the maximum thermal resistance of the heat sink in parallel with the case-ambient resistance for the IC package, we can simply subtract the junction-case resistance  $(14^{\circ}\text{C/W})$  from the total allowable resistance  $(34.7^{\circ}\text{C/W})$  to get the result,  $34.7^{\circ}\text{C/W} - 14^{\circ}\text{C/W} = 20.7^{\circ}\text{C/W}$ . The case-ambient thermal resistance for the IC package is the difference between the supplied values for the junction-case and junction-ambient  $(80^{\circ}\text{C/W} - 14^{\circ}\text{C/W} = 66^{\circ}\text{C/W})$ . Finally, by using the formulas for parallel resistors (a big benefit of using the electrical analogy for thermal systems), we can develop an expression for the required thermal resistance of the heat sink:

$$R_{\text{total}} = \frac{R_{\text{case}}R_{\text{sink}}}{R_{\text{case}} + R_{\text{sink}}}$$

(17.1)

$$R_{\rm sink} = \frac{R_{\rm case} R_{\rm total}}{R_{\rm case} - R_{\rm total}}$$

(17.2)

Inserting the numbers for this example, we calculate a required heat sink resistance of at most 30.2°C/W. With this value in hand, we can search for heat sinks that mount to a 16-pin DIP package and provide a thermal resistance of less than 30.2°C/W. Figure 17.21 shows an example of such a heat sink which is specified for 20°C/W.

#### **17.8 HOMEWORK PROBLEMS**

- **17.1** If you wanted to drive an LED to the maximum possible brightness with the output of a 7400, would you arrange it so that the LED was on when the 7400's output was in the low state or the high state? Use worst-case design principles and quote specifications from Figure 17.2 to support your answer.

- **17.2** If you wanted to drive an LED to the maximum possible brightness with the output of a 74HC04, would you arrange it so that the LED was on when the 74HC04's output was in the low state or the high state? Use worst-case design principles and quote specifications from Figure 17.3 to support your answer.

- **17.3** If an LED is to be driven from either a 7400 or a 74HC04, which would you expect to produce the greater LED light output? Use worst-case design principles and quote specifications from Figures 17.2 and 17.3 to support your answer.

- 17.4 If the outputs from two LM339A devices are to be used in a wired OR configuration to drive a single input of an MC9S12 family device (use the specifications from Figures 17.8 and 16.1), what are the minimum and maximum values for the pull-up resistor? Choose from among commercially available 5% tolerance resistors.

- **17.5** Using the ULN2003A specifications from Figure 17.12, what is the minimum required input voltage to be able to support an output current of 200 mA?

FURTI