Orcad<sup>®</sup> Layout

**Getting Started**

Copyright © 1985-2000 Cadence Design Systems, Inc. All rights reserved.

#### Trademarks

Allegro, Ambit, BuildGates, Cadence, Cadence logo, Concept, Diva, Dracula, Gate Ensemble, NC Verilog, OpenBook online documentation library, Orcad, Orcad Capture, PSpice, SourceLink online customer support, SPECCTRA, Spectre, Vampire, Verifault-XL, Verilog, Verilog-XL, and Virtuoso are registered trademarks of Cadence Design Systems, Inc.

Affirma, Assura, Cierto, Envisia, Mercury Plus, Quickturn, Radium, Silicon Ensemble, and SPECCTRAQuest are trademarks of Cadence Design Systems, Inc.

Alanza is a service mark of Cadence Design Systems, Inc.

All other brand and product names mentioned herein are used for identification purposes only and are registered trademarks, trademarks, or service marks of their respective holders.

Part Number 60-30-645

Second edition 31 May 2000

| Cadence PCB Systems Division (PSD) offices |  |  |  |  |  |  |  |  |

|--------------------------------------------|--|--|--|--|--|--|--|--|

|                                            |  |  |  |  |  |  |  |  |

|                                            |  |  |  |  |  |  |  |  |

|                                            |  |  |  |  |  |  |  |  |

|                                            |  |  |  |  |  |  |  |  |

|                                            |  |  |  |  |  |  |  |  |

| 1                                          |  |  |  |  |  |  |  |  |

| n/technical/technical.asp                  |  |  |  |  |  |  |  |  |

| n/technical/email_support.asp              |  |  |  |  |  |  |  |  |

|                                            |  |  |  |  |  |  |  |  |

Cadence PCB Systems Division 13221 SW 68th Parkway, Suite 200 Portland, OR 97223

## Contents

|           | Before you begin    vii      Welcome to OrCAD    vii      How to use this guide    viii      Symbols and conventions    viii                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 | Board design tasks 1                                                                                                                                                                                           |

|           | Typical board design tasks2Board design flow3                                                                                                                                                                  |

| Chapter 2 | Creating a board 5                                                                                                                                                                                             |

|           | Methods to create a board6Creating a board from scratch7Creating a board using a board template8Importing a board using the DXF to Layout translator10Importing a board using the PRO-E to Layout translator12 |

| Chapter 3 | Setting up board parameters 15                                                                                                                                                                                 |

|           | Creating a board outline16Setting units of measurement17Setting system grids18Adding mounting holes to a board21Defining the layer stack22Defining global spacing values23Defining padstacks25Using vias26     |

| Chapter 4 | Placing components 29                                                                                                                                                                                          |

|           | Preparing the board for component placement    30      Checking the board, place, and insertion outlines    30      Checking the place grid    31                                                              |

#### Contents

|           | Checking mirror layers and library layers32Weighting and color-coding nets33Checking gate and pin information34Securing preplaced components on the board35Creating height or group keepins and keepouts36Loading a placement strategy file38Disabling the power and ground nets39Selecting the next components for placement40Placing component groups40Minimizing connections to optimize placement41Checking placement41Using Placement Spacing Violations42Using the density graph43Viewing placement statistics44 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 5 | Routing critical nets45Push-and-shove routing46Interactive routing46Before you begin routing47Routing the board manually47Routing the board outline, via definitions, and routing and via grids 48Loading a routing strategy file49Changing board density using routing strategy files49Routing power and ground50Fanout52Verifying plane layer connections and disabling power and ground nets                                                                                                                        |

|           | 54Using interactive push-and-shove routing55Using shove track mode55Checking routing57Using Route Spacing Violations57Viewing routing statistics58                                                                                                                                                                                                                                                                                                                                                                     |

| Chapter 6 | Finishing the board59Checking design rules60Investigating errors61Removing violations62Cleaning up your design62Renaming components63Back annotating63                                                                                                                                                                                                                                                                                                                                                                 |

| Post processing . | • |  |  |  | • |  |  |  |  |  |  |  |  |  |  |  |  | 64 |

|-------------------|---|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|--|----|

| Creating reports  |   |  |  |  |   |  |  |  |  |  |  |  |  |  |  |  |  |    |

Index 67

Contents

## Before you begin

## Welcome to OrCAD

OrCAD offers a total solution for your core design tasks: schematic- and VHDL-based design entry; FPGA and CPLD design synthesis; digital, analog, and mixed-signal simulation; and printed circuit board layout. What's more, OrCAD's products are a suite of applications built around an engineer's design flow—not just a collection of independently developed point tools.

## How to use this guide

• This guide is designed so you can quickly find the information you need to use OrCAD Layout.

## Symbols and conventions

OrCAD printed documentation uses a few special symbols and conventions.

| Notation        | Examples                                     | Description                                                                                                                                                                                                |

|-----------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ctrl)+R         | Press Ctrl)+R                                | Means to hold down the $Ctrl$ key while pressing $\mathbb{R}$ .                                                                                                                                            |

| (Alt), (F), (O) | From the File menu, choose Open (Alt), F, O) | Means that you have two options. You<br>can use the mouse to choose the Open<br>command from the File menu, or you<br>can press each of the keys in<br>parentheses in order: first Alt, then F,<br>then O. |

| Monospace font  | In the Part Name text box, type PARAM.       | Text that you type is shown in monospace font. In the example, you type the characters $\mathbb{P}$ , $\mathbb{A}$ , $\mathbb{R}$ , $\mathbb{A}$ , and $\mathbb{M}$ .                                      |

| UPPERCASE       | In Capture, open CLIPPERA.DSN.               | Path and filenames are shown in<br>uppercase. In the example, you open<br>the design file named CLIPPERA.DSN.                                                                                              |

| Italics         | In Capture, save <i>design_name</i> .DSN.    | Information that you are to provide is<br>shown in italics. In the example, you<br>save the design with a name of your<br>choice, but it must have an extension of<br>.DSN.                                |

## **Board design tasks**

This manual was created especially to address specific tasks that electronic design engineers perform. Depending on where you fall in the task list below, you'll use some or all of Layout's capabilities to accomplish your board design tasks. The "See" notation below each bullet item directs you to the chapters or sections in this manual that pertain to your specific tasks.

- Designing a board from start to finish.

See *The entire manual.*

- Reviewing boards that others have created. See *Checking placement, Checking routing.*

- Specifying placement and critical routing.

See *Placing components, Checking placement, Routing critical nets, and Checking routing.*

### For instructions on creating a netlist in Capture, see the Capture documentation.

For information on using GerbTool, see the OrCAD Layout GerbTool User's Guide.

## Typical board design tasks

Typical board design tasks include the following:

- Creating the board. Using Capture, you create a netlist from your schematic that may include your design rules to guide logical placement and routing, then load the netlist into Layout.

- Specifying board parameters. You specify global settings for the board, including units of measurement, grids, and spacing. In addition, you create a board outline and define the layer stack, padstacks, and vias.

- Placing components and checking the placement. You use the component tool to manually place components on the board individually or in groups. You then check the placement using placement information from a variety of sources.

- Routing the board and checking the routing. You route the board, and can take advantage of *push-and-shove* (a routing technology), which moves tracks to make room for the track you are currently routing. You then check the routing using routing information from a variety of sources.

- Finishing the board. Layout supplies an ordered progression of commands on the Auto menu for finishing your design. These commands include Design Rule Check, Cleanup Design, Rename Components, Back Annotate, Run Post Processor, and Create Reports.

- Layout includes GerbTool, which is a full-featured CAM tool, including a Gerber editor, that reads and writes all standard Gerber formats and IPC-356. GerbTool has features for automatic teardropping, panelization, venting and thieving, and removal of unused pads and silkscreen on pads. These processes are used to improve manufacturability.

Layout also includes Visual CADD, which is a two-dimensional drafting tool you can use for your mechanical design needs. Visual CADD facilitates design and drafting by providing tools for creating board outlines, height keepins and keepouts, and similar objects, as well as single or double lines, circles, regular and irregular polygons, and more. Visual CADD imports and exports .DWG, .DXF, and .GCD files.

For information on using Visual CADD, see the OrCAD Layout Visual CADD User's Guide or the OrCAD Layout Visual CADD Tutorial manual.

## **Board design flow**

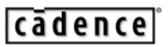

The flowchart below illustrates a typical board design flow.

## **Creating a board**

Before you begin creating a board, read the following to become more familiar with the types of files you may be working with.

A *netlist* file (.MNL) describes the interconnections of a schematic design using the names of the nets, components, and pins. A netlist contains the following:

- Footprint names

- Electrical packaging

- Component names

- Net names

- The component pin for each net

- Net, pin, and component property information

For instructions on creating a netlist in Capture, see the Capture documentation.

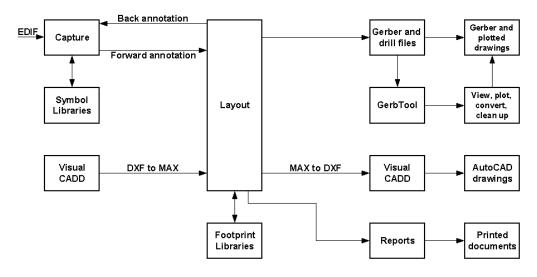

Other board criteria, such as units of measurement, system grids, and spacing values can be saved with a board template for use with future boards. For instructions on creating a custom board template (.TPL), see *Custom templates* in *Chapter 4: Setting up the board* in the *OrCAD Layout User's Guide*. A technology template (.TCH) specifies the characteristics of a board, including manufacturing complexity and component type. Technology templates can also include the layer structure, grid settings, spacing instructions, and a variety of other board criteria. The technology templates supplied with Layout are documented in Appendix A: Understanding the files used with Layout in the OrCAD Layout User's Guide.

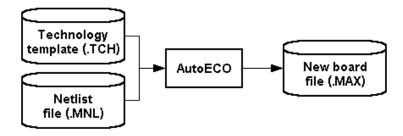

A *board template* (.TPL) combines a board outline and possible mounting holes, edge connectors, and other physical board objects merged with Layout's default technology template, DEFAULT.TCH. The board templates supplied with Layout are illustrated in the *OrCAD Layout Footprint Libraries* manual.

A *board* file (.MAX) contains all of the board's physical and electrical information.

## Methods to create a board

Create a board from scratch

- Use a board template

- Import your board to Layout using the DXF to Layout translator

- Import your board to Layout using the PRO-E to Layout translator

#### Creating a board from scratch

#### To create a board from scratch

- 1 Ensure that a netlist with all footprints and other necessary information has been created.

- 2 Create a directory in which the schematic design, netlist, and board will coexist and put the schematic design (if you have it) and netlist in it. OrCAD provides a directory (ORCADWIN\LAYOUT\DESIGN) for this purpose.

- **3** From the Layout session frame's File menu, choose New. The Load Template File dialog box displays.

- 4 Select a technology template (.TCH), then choose the Open button. The Load Netlist Source dialog box displays.

- 5 Select a netlist file (for example, *design\_name*.MNL), then choose the Open button. The Save File As dialog box displays.

- 6 Specify a name for the new board (for example, *design\_name*.MAX), then choose the Save button. The AutoECO process begins.

- 7 If necessary, respond to the Link Footprint to Component dialog box (choose the dialog box's Help button for an explanation of the dialog box's options).

- 8 Draw a board outline using the steps in *To create a board outline* on page 24.

**Tip** If your board uses metric units, use METRIC.TCH.

Creating a board using a board template

Tip One benefit of using a board template (.TPL) is that, in addition to containing all the information in DEFAULT.TCH, a board template contains a board outline, saving you the task of having to draw one yourself.

**Note** To determine which of the board templates (.TPL) you want to use, you can view their illustrations in the OrCAD Layout Footprint Libraries manual, or you can do the following:

> From the Layout session frame's File menu, choose Open. The Open Board dialog box displays.

> Change to the ORCADWIN\LAYOUT\DATA directory, change the Files of type to All Files, select a board template (.TPL), then choose the Open button. The board template displays in Layout.

Inspect the board template to determine if you want to use it for your new board. If not, repeat the process as many times as necessary to find a .TPL file you want to use, then close the file.

Note If a board template has components (such as edge connectors), then you must have matching parts with matching reference designators in your schematic design in order for Layout to assign nets to the components. If the reference designators do not match, Layout will bring in a new part, and the components that are part of the board template will not have nets assigned to them.

If you find a board template that is similar to what you want to use but needs some modification, you can customize it and save it under another name using a .TPL extension. For instructions on creating a custom board template, see *Custom templates* in *Chapter 4, Setting up the board* in the *OrCAD Layout User's Guide*.

#### To create a board using a board template

- 1 Ensure that a netlist with all footprints and other necessary information has been created.

- 2 Create a directory in which the schematic design, netlist, and board will coexist and put the schematic design (if you have it) and netlist in it. OrCAD provides a directory (ORCADWIN\LAYOUT\DESIGN) for this purpose.

- **3** From the File menu, choose New. The Load Template File dialog box displays.

- 4 Select a board template (.TPL), then choose the Open button. The Load Netlist Source dialog box displays.

- 5 Select a netlist file (for example, *design\_name*.MNL), then choose the Open button. The Save File As dialog box displays.

- 6 Specify a name for the new board (for example, *design\_name*.MAX), then choose the Save button. The AutoECO process begins.

- 7 If necessary, respond to the Link Footprint to Component dialog box (choose the dialog box's Help button for an explanation of the dialog box's options).

- 8 AutoECO finishes, and you see the components in the design window.

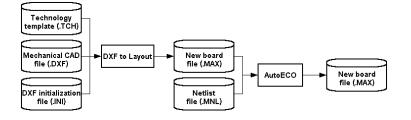

Importing a board using the DXF to Layout translator

#### To import a board using the DXF to Layout translator

- 1 Ensure that a netlist with all footprints and other necessary information has been created.

- 2 Create a directory in which the schematic design, netlist, and board will coexist and put the schematic design (if you have it) and netlist in it. OrCAD provides a directory (ORCADWIN\LAYOUT\DESIGN) for this purpose.

- 3 Create a board outline in Visual CADD (or in another mechanical CAD application), save it (and any other pertinent floor planning information) as a .DXF file, then put the .DXF file in the same directory as your schematic design and netlist.

- 4 From Layout's session frame, choose File, then Import, then DXF to Layout. The DXF to MAX dialog box displays.

- 5 In the Input DXF File text box, use the Browse button to locate and select the .DXF file you created in step 3, then choose the Open button.

- **Note** If the .DXF file was created using millimeters, the DXF to MAX result will be a metric board (.MAX). Therefore, your netlist must also be in millimeters, because Layout will not read in a netlist created in inches if the board is in millimeters (and vice versa).

- **6** In the Output Layout File text box, supply a name for the output .MAX file.

For instructions on creating a board outline and saving it as a .DXF file in Visual CADD, and on modifying the MAXDXF initialization file, which specifies the mapping of data between DXF and Layout formats, see the OrCAD Layout Visual CADD Tutorial. For instructions on using Visual CADD, see the OrCAD Layout Visual CADD User's Guide.

- 7 Verify that MAXDXF.INI displays in the DXF.INI File text box and that DEFAULT.TCH displays in the Technology File text box, then choose the Translate button. Layout combines the files and displays the results of the translation in a text editor, such as Notepad. Close the text editor when you're finished viewing the translation results.

- 8 From Layout's session frame, choose File, then Open. The Open Board dialog box displays.

- **9** Locate and select the .MAX file that you supplied the name for in step 6, then choose the Open button. The board displays in Layout.

- 10 Review the board, ensuring that the datum is where you want it and the drill chart is in an acceptable location (for example, to the right of the board outline, to keep it out of the way of components that will load with the netlist). When the board is as you want it, save it (using a .MAX extension) and exit Layout.

- **Tip** You can save the board you've reviewed in step 10 as a board template (.TPL), so that you can reuse it. For instructions on creating a custom board template, see Custom templates in Chapter 4, Setting up the board in the OrCAD Layout User's Guide.

- 11 From the Layout session frame's File menu, choose New. The Load Template File dialog box displays.

- **12** Change the Files of type to Board (\*.MAX), locate and select the .MAX file you saved in step 10, then choose the Open button. The Load Netlist Source dialog box displays.

- **13** Select a netlist file (for example, *design\_name*.MNL), then choose the Open button. The Save File As dialog box displays.

- 14 Specify a name for the new board (for example, *design\_name*.MAX), then choose the Save button. The AutoECO process begins.

- 15 If necessary, respond to the Link Footprint to Component dialog box (choose the dialog box's Help button for an explanation of the dialog box's options).

For instructions on moving the datum, see the final step of *Creating a board outline* on page 24. For instructions on moving the drill chart, see *Moving the drill chart* in *Chapter 11, Post processing* in the *OrCAD Layout User's Guide.*  **16** AutoECO finishes, and you see the components in the design window.

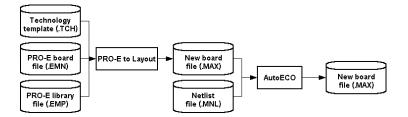

## Importing a board using the PRO-E to Layout translator

The PRO-E to Layout translator can be used to translate Pro/ENGINEER Intermediate Drawing Format (IDF) files into Layout. Note that IDF files come in pairs: the board file (.EMN) contains the board outline, keepouts, and component placements, while the library file (.EMP) contains additional data for each component placed in the board file, such as the component placement outline and the component height.

To import a board using the PRO-E to Layout translator

- 1 Ensure that a netlist with all footprints and other necessary information has been created.

- 2 Create a directory in which the schematic design, netlist, and board will coexist and put the schematic design (if you have it) and netlist in it. OrCAD provides a directory (ORCADWIN\LAYOUT\DESIGN) for this purpose.

- 3 Save your Pro/ENGINEER design in IDF format, using an .EMN extension for the board file and an .EMP extension for the library file, then put the .EMN and .EMP files in the same directory as your schematic design and netlist.

- 4 From Layout's session frame, choose File, then Import, then PRO-E to Layout. The PRO-E to Layout dialog box displays.

- 5 In the Input IDF Board File text box, supply a name for the Pro/ENGINEER board file (.EMN).

- 6 In the Input IDF Library File text box, supply a name for the Pro/ENGINEER library file (.EMP).

- Tip Mechanical Engineers will sometimes create a board outline, height restriction zones, voids, and route keepouts in a tool like Pro/ENGINEER, then transmit that information to the Electrical Engineer using an IDF Board file. Since there is no component placement data, there will not be an IDF Library file. In this case, simply leave the text box for the Input IDF Library File blank.

- 7 In the Input Technology or Layout File text box, supply a name for the technology or layout file.

- Tip If you are creating a new Layout file, choose a technology file (.TCH) to use as a template. If you are bringing back to Layout a board that has undergone thermal analysis, put the name of the original Layout board file (.MAX) you modeled in the Input Technology or Layout File text box. That way, if you have shifted component placements to meet your heat dissipation goals, the components in your original Layout board file will be moved to their new locations.

- 8 In the Output Layout File text box, supply a name for the output .MAX file.

- **9** Select the following options as desired, then choose the Translate button.

**Overwrite existing files** Select this option if you want the output files to overwrite existing files without first prompting for your permission.

**Center placed components** If the placement origin for critical components as defined by the Mechanical Engineer does not match the placement origin as defined by the Electrical Engineer, select this option, which causes the centroid of the Mechanical Engineer's part to overlay the centroid of the Electrical Engineer's part. Note, though, that the reference designator used for the part must match the reference designator specified in your netlist. If it does not, edit the part once you have translated the design into Layout format, but before you load your netlist. Once the reference designator matches your netlist, loading the netlist provides the part with the required footprint, silkscreen, and electrical connectivity information.

**Ignore all components** Select this option if you want to discard the component placement information in your IDF Library file.

**Do not update board outline or voids** Select this option if you changed the board outline (for example, during thermal modeling), but you want to keep the board outline that's in your original Layout file.

- **10** From the Layout session frame's File menu, choose New. The Load Template File dialog box displays.

- 11 Change the Files of type to Board (\*.MAX), locate and select the new .MAX file, then choose the Open button. The Load Netlist Source dialog box displays.

- 12 Select a netlist file (for example, *design\_name*.MNL), then choose the Open button. The Save File As dialog box displays.

- 13 Specify a name for the new board (for example, *design\_name*.MAX), then choose the Save button. The AutoECO process begins.

- 14 If necessary, respond to the Link Footprint to Component dialog box (choose the dialog box's Help button for an explanation of the dialog box's options).

- **15** AutoECO finishes, and you see the components in the design window.

## Setting up board parameters

In Layout, you should set up the board's parameters before you begin placing components. The parameters are listed below, but not all of them may be needed for your board.

- Create a board outline

- Set the units of measurement

- Set system grids

- Add mounting holes

- Define the layer stack

- Set global spacing

- Define padstacks

- Define vias

**Note** All of the items listed above can be saved to board templates. For instructions on creating a custom board template (.TPL), see Custom templates in Chapter 4: Setting up the board in the OrCAD Layout User's Guide.

For information on setting net properties, and on the options in the Edit Net dialog box, see Chapter 4: Setting up the board in the OrCAD Layout User's Guide.

## Creating a board outline

**Note** Layout requires exactly one board outline, on the global layer.

#### To create a board outline

- 1 From the Tool menu, choose Dimension, then choose Datum. Click on the lower left corner of the board outline to place the datum (to provide a starting grid for component placement). Press HOME to redraw the screen.

- **Note** Placing the datum in the lower-left corner of the board outline gives you positive X, Y coordinates, while placing it in other corners gives you negative coordinates (in your reports and post processing results). In addition, since the board datum is used for all grids, if you move the datum after component placement, your place, routing, and via grids will all be affected. And, you may have difficulty replacing the datum at the precise location you moved it from.

- 2 Choose the obstacle toolbar button.

- **3** From the pop-up menu, choose New, then from the pop-up menu, choose Properties. The Edit Obstacle dialog box displays.

- 4 From the Obstacle Type drop-down list, select Board outline.

- 5 In the Width text box, enter a value for the outline's width.

**Tip** Layout has a 50 mils default board outline width, in order to provide clearance on plane layers for the copper of the plane to the edge of the board. One-half of the width is the pullback (25 mils in the default width), so set the board outline's width to two times the pullback you would like. The cut is made down the center of the board outline obstacle.

- 6 From the Obstacle Layer drop-down list, select Global Layer, then choose the OK button. The Edit Obstacle dialog box closes.

- 7 Move to the point on the board at which you want to start drawing the outline, then click the left mouse button to insert the first corner.

- **Note** Since a board outline must be a closed polygon, Layout automatically begins forming a closed area after you insert the first corner of the board outline, and automatically closes the polygon for you if you don't close it yourself.

- 8 Continue clicking the left mouse button to insert corners.

- **9** After you click to insert the last corner, choose Finish from the pop-up menu. Layout automatically completes the board outline.

**Tip** If you zoom in while drawing, you can press c to put your current cursor location in the center of the screen.

## Setting units of measurement

In Layout, you can set numeric data to display in mils, inches, microns, millimeters, or centimeters. You can change these values as needed (for example, you can route the board in inches or mils, then confirm pad locations within footprints in millimeters).

**Note** If your board uses metric units, you can achieve the best precision by using the METRIC.TCH technology template. With your board open in Layout, choose Load from the File menu, select METRIC.TCH, then choose the Open button. After METRIC.TCH loads, save your board.

#### To set measurement units

- 1 Open your board in Layout.

- 2 From the Options menu, choose System Settings. The System Settings dialog box displays.

- **3** Select mils, inches, microns, millimeters, or centimeters.

- 4 Choose the OK button.

- **Note** Once you decide on a measurement unit, you should stick with it and not change it in either your board or your schematic. If you back annotate to your schematic, then change to another measurement unit, it may cause board corruption problems.

## Setting system grids

Using the System Settings dialog box, you can set five distinct grid settings. The grid values that you assign determine the resolution of the pointer location coordinates given in the status bar in the lower left corner. For example, if the obstacle tool is selected and the Place grid is set to 100 mils, the coordinates that display are accurate to 100 mils.

Grid values are in user-specified units that you set in the Display Units group box in the System Settings dialog box. If you want to use fractions in your grid values, enter a space character following the integer and use a forward slash as the division character (for example, 8 1/3). You can also use decimals for rational numbers.

- **Tip** Here are some rules of thumb for setting the grids:

- For efficient routing performance, the routing grid and via grid should have the same value.

- The place grid must be a multiple of the routing and via grids.

- The routing grid should never be less than 5 mils.

- The detail grid can be set as low as 1 mil for better resolution.

- Components are placed on the place grid using the component datum, which is typically pad 1 (unless the component has been modified).

#### To set system grids

- 1 From the Options menu, choose System Settings. The System Settings dialog box displays.

- 2 Set these options, then choose the OK button.

**Visible grid** Assigns a display grid based on the X and Y coordinates (for example, if you're using mils, a setting of 200 would place a grid dot at every 200 mils).

**Detail grid** Assigns a drawing grid (for lines and text) based on the X and Y coordinates.

**Place grid** Assigns a component placement grid based on the X and Y coordinates. For greatest routing efficiency, this value needs to be a multiple of the routing grid. The datum, or origin, of footprints is constrained to this grid.

**Routing grid** Assigns a grid used for routing (see the routing grid chart below for suggested settings).

**Via grid** Assigns a grid upon which you or the router can place vias.

The following chart is a synopsis of routing grids and how to use them in Layout.

| Routing                  | grid                                                                | Uses                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compati                  | ble grids 25,                                                       | , 12 <sup>1</sup> /2, 8 <sup>1</sup> /3, and 6 <sup>1</sup> /4:                                                                                                                                                                                                                                                                                                                                                                         |

| 25, 12 <sup>1</sup> /    | /2                                                                  | Use for less dense (usually .45 density or greater)<br>through-hole and SMT boards, and for routing<br>one track between IC pins.                                                                                                                                                                                                                                                                                                       |

| <b>8</b> <sup>1</sup> /3 |                                                                     | Use for a secondary grid on through-hole boards,<br>and for a primary grid on SMT boards. Use as a<br>secondary grid with 25 mils grid only if the 25<br>mils grid initially routes 95% or better.                                                                                                                                                                                                                                      |

| <b>6</b> <sup>1</sup> /4 |                                                                     | Use for 6/6 technology, or denser one-between boards.                                                                                                                                                                                                                                                                                                                                                                                   |

| Compati                  | ble grids 20                                                        | and 10:                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20                       |                                                                     | Use for through-hole boards only. This is the most efficient way to route two tracks between IC pins.                                                                                                                                                                                                                                                                                                                                   |

| 10                       |                                                                     | Use for through-hole, two-between boards placed<br>on a 50 mils grid, and for SMT boards using 10/10<br>technology. Also, use for special cases when a 20<br>mils grid causes off-grid jogs.                                                                                                                                                                                                                                            |

| Compati                  | ble grids 25,                                                       | 20, and 10:                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5                        |                                                                     | Use for extremely dense SMT boards that use 5 mils spacing and 5 mils track width (for mixed inch and metric technologies).                                                                                                                                                                                                                                                                                                             |

| Note                     | same boar<br>the final r<br>(for instar<br>completion<br>dense, via | ible grids (such as 20 and 25) should not be mixed on the<br>rd. If you find it necessary to do so, use a 5 mils grid for<br>eroute pass. Also, a via grid smaller than the routing grid<br>nce, a 5 mils via grid on a 25 mils grid board) increases<br>n on difficult SMT boards. Of course, if a board is very<br>a sizes should by reduced to the minimum size possible,<br>are responsible for much of the channel blockage during |

# Adding mounting holes to a board

You can add mounting holes to a board, and you can also save them in a board template (.TPL). Once you add the mounting holes to the board, define them as non-electrical. You can still attach non-electrical mounting holes to the ground net. It's just that the non-electrical flag keeps the ECO process from removing them.

#### To add mounting holes to a board

- 1 Choose the component toolbar button.

- 2 From the pop-up menu, choose New. The Add Component dialog box displays.

- **3** Choose the Footprint button. The Select Footprint dialog box displays.

- 4 In the Libraries group box, select LAYOUT.LLB. Use the Add button, if necessary, to add this library to the list of available libraries. (LAYOUT.LLB resides in the LIBRARY directory.)

- 5 In the Footprints group box, select a mounting hole (OrCAD provides three: MTHOLE1, MTHOLE2, and MTHOLE3). Choose the OK button to close the Select Footprint dialog box.

- 6 Select the Non-Electric option, then choose the OK button to close the Add Component dialog box. The mounting hole attaches to your cursor.

- 7 Place the mounting hole by clicking the left mouse button.

**Tip** To have a mounting hole thermal into the plane layer, attach it to the net that is shorted to the plane layer. You can do this after placement.

If you don't want a pad on the top, bottom, and inner layers, but need clearance on the plane layers, place pads that are 1 mil in diameter on the top, bottom, and inner layers. These 1 mil pads will be seen by SmartRoute and avoided, and will be drilled out when drill holes are drilled through the board. For the plane layers, you need to define pads that are 15 mils larger than the drill hole, to provide adequate clearance from the drill. Pad size on plane layers is used to define clearance. Plane layers are represented in the inverse, in Layout.

## Defining the layer stack

For instructions on how to copy a padstack layer to a newly defined layer (for example, an additional plane layer), see Copying padstack layers in Chapter 14, Creating and editing footprints in the OrCAD Layout User's Guide. Routing and documentation layers are defined in the Layers spreadsheet. Using the spreadsheet, you can define the number of routing layers that will be used for the board. If you plan to have a board with four routing layers (TOP, BOTTOM, INNER1, and INNER2) and two plane layers (POWER, GROUND), then you need to define the layers in a technology template (.TCH) or a board template (.TPL).

Tip It is better to have too many routing or plane layers defined than too few (if you're unsure of the number you will need) before reading in a netlist, because you can decrease the number of the layers later, by designating them as unused.

After defining the layer stack, you can save the information to a board template (.TPL) for use in future boards.

#### To define layers for routing

- 1 Choose the spreadsheet toolbar button, then choose Layers. The Layers spreadsheet displays.

- 2 Review the type assignments for the routing layers and double-click in the Layer Name column of a layer you want to modify. The Edit Layer dialog box displays.

- 3 In the Layer Type group box, select the desired option (for example, to disable a layer for routing, select Unused Routing; to define an additional plane layer, select Plane Layer).

- 4 If you changed a routing layer to a plane layer, change the Layer LibName to PLANE.

- 5 Choose the OK button.

## **Defining global spacing values**

Global spacing values set rules for spacing between the various objects on the board. You can define global spacing values for the board using the Edit Spacing dialog box, which is accessed from the Route Spacing spreadsheet (choose the spreadsheet toolbar button, choose Strategy, then choose Route Spacing). You can save spacing requirements in a board template (.TPL). Uniform spacing requirements per layer reduce processing time.

**Tip** To globally assign the same spacing to all layers, double-click in the Layer Name title cell in the Route Spacing spreadsheet. When the Edit Spacing dialog box displays, enter a value in the appropriate text box (for example, enter a value for Track to Track Spacing), then choose the OK button.

**Note** Do not delete layers from the Layers spreadsheet. To disable a layer, double-click on it, then specify it as Unused Routing in the Edit Layer dialog box.

#### To define global spacing values

- 1 Choose the spreadsheet toolbar button, choose Strategy, then choose Route Spacing. The Route Spacing spreadsheet displays.

- 2 Double-click on the layer you want to modify. The Edit Spacing dialog box displays.

- **3** Set these options, then choose the OK button.

**Track to Track Spacing** Tracks are defined as any routed track and copper obstacles (such as keepouts and place outlines). Track-to-track spacing specifies the minimum space required between tracks of different nets, and between tracks and obstacles of different nets.

**Track to Via Spacing** Track-to-via (and obstacle-to-via) spacing specifies the minimum space required between vias and tracks of different nets.

**Track to Pad Spacing** Track-to-pad (and obstacle-to-pad) spacing specifies the minimum space required between pads and tracks of different nets.

**Via to Via Spacing** Specifies the minimum space required between vias of different nets.

**Via to Pad Spacing** Specifies the minimum space required between pads and vias of the same net (as well as different nets, which is the usual case). For instance, to keep a distance of 25 mils between your SMT pads and the fanout vias connected to the pads, set Via to Pad Spacing to 25.

**Pad to Pad Spacing** Specifies the minimum space required between pads of different nets.

## **Defining padstacks**

Padstacks define the pads of the footprint. They possess properties on each layer of the board, such as shape and size. If you are using the standard Layout footprint libraries, or if you have made your own footprints using Layout standards, you have used padstacks T1 through T7 to create most of the standard through-hole components in your library.

Note Don't name your custom padstacks using the names T1 through T7, because they will be overwritten by technology template padstacks whenever you load a technology template. Also, be sure to define through-hole padstacks on all layers, including unused layers. Otherwise, you may unintentionally create blind or buried vias. Surface-mount pads, on the other hand, are not defined on internal layers.

You can create new padstacks when you set up the board, or in the footprint library. You must define padstacks before you assign them to footprints. You can define new padstacks by copying and editing existing padstacks in the Padstacks spreadsheet. Then, you can assign them to footprints or footprint pins. After you create new padstacks, you can save them in a board template (.TPL) for use with future boards.

#### To create a new padstack

- 1 Choose the spreadsheet toolbar button, then choose Padstacks. The Padstacks spreadsheet displays.

- 2 Select a padstack and choose Properties from the pop-up menu. The Edit Padstack dialog box displays.

- **3** Type a new name for the padstack in the Padstack text box, edit the other options to change the size or shape as desired, then choose the OK button.

- 4 Make specific layer definitions for the padstack for the drill and plane layers.

For information on assigning padstacks to footprints or footprint pins, and on editing padstacks, see Chapter 14, Creating and editing footprints in the OrCAD Layout User's Guide.

## Using vias

You can define the types of vias that you want to use when routing your board, either vias or *free vias*. Free vias (denoted by the letters FV) are ignored by Layout's board cleanup routines, so you can place them on your board and have them stay there, as long as they are attached to a net. They are preserved through AutoECO, unless the net or routed track they are connected to is entirely deleted or removed from the board. Layout regards free vias as stand-alone components: you can shove them, place them in isolation (free of tracks), or connect them to multiple tracks on the same net. You can use free vias for special purposes, such as zero-length fanouts of ball grid array (BGA) components and the "stitching" of plane layers.

Layout provides one defined via and fifteen undefined vias. You define additional vias in the Edit Padstack dialog box (from the Padstacks spreadsheet) to make them available for routing. Then, using the Assign Via dialog box (from the Nets spreadsheet), you can assign a specific via to be used when routing a particular net.

**Note** Selecting a via for a particular net does not prohibit any other net from using that via. The assignments made in the Assign Via dialog box simply override, for selected nets, the Use All Via Types option set in the Route Settings dialog box (from the Options menu, choose Route Settings). Therefore, you can select the Use All Via Types option and still assign specific vias to specific nets using the Assign Via dialog box.

For example, if you want to use Via 1 for all of your signal routing, but you want to restrict VCC to Via 2 and GND to Via 3, you would start by selecting the Use All Via Types option to make the defined vias available for routing. Then you would select VCC in the Nets spreadsheet, choose Assign Via per Net from the pop-up menu, and select Via 2 in the Assign Via dialog box. Finally, you would select GND in the Nets spreadsheet, choose Assign Via per Net from the pop-up menu, and select Via 3 in the Assign Via dialog box. Tip If you don't select the Use All Via Types option in the Route Settings dialog box, you must specifically assign vias to nets that need their via types restricted. Otherwise, the router chooses what it considers the "best" via, using its standard criteria: the layer(s) the via is defined on and its size compared to track size.

#### To make a via available for general routing

- 1 Choose the spreadsheet toolbar button, then choose Padstacks. The Padstacks spreadsheet displays.

- 2 Select an unused via and choose Properties from the pop-up menu. The Edit Padstack dialog box displays.

- **3** Type a new name for the via (for a free via, for example, you could use the name POWERVIA) and edit the other options to change the size or shape as desired, then choose the OK button.

- 4 From the Options menu, choose Route Settings. The Route Settings dialog box displays.

- 5 Select the Use All Via Types option and choose the OK button.

- **6** Close the Padstacks spreadsheet.

#### To assign a via to a net

- 1 Choose the spreadsheet toolbar button, then choose Nets. The Nets spreadsheet displays.

- 2 Select the net to which you want to assign a via.

- 3 From the pop-up menu, choose Assign Via per Net.

- 4 Select the desired via and choose the OK button.

- 5 Close the Nets spreadsheet.

- **Note** You don't have to select the Use All Via Types option in the Route Settings dialog box to assign a via to a particular net.

For information on changing the definition of a via, see *Changing vias* in *Chapter 8*, *Routing the board* in the *OrCAD Layout User's Guide*.

#### To place a via

- 1 Choose one of the routing toolbar buttons.

- 2 Begin routing the net on which you want to place a via.

- **3** Click the left mouse button to place a vertex (a corner).

- From the pop-up menu, choose Add Via.*or*From the pop-up menu, choose Add FreeVia.

# **Placing components**

Once you have set up your board by following the procedures in Chapter 3, *Setting up board parameters*, you can begin component placement.

# Preparing the board for component placement

Before you begin placing components manually, it is important to set up the board properly. Use the list below as a preplacement checklist.

- Check the board, place, and insertion outlines

- Check the place grid

- Check mirror layer or library layer settings

- Weight and color-code nets

- Check gate and pin data

- Check preplaced components and secure them on the board using the Lock or Fix commands

- Create component height keepins and keepouts, or group keepins and keepouts

## Checking the board, place, and insertion outlines

The board outline is used by Layout to determine the overall board placement boundary, and it must be present on the global layer of the board. It can be defined as part of the board template, or you can create it when you set up the board.

A place outline defines the extent of the area that is reserved for a component's placement. Each footprint must have one. Layout uses place outlines to determine whether any component spacing violations occur during placement. A place outline can be assigned a height and a layer. One or more place outlines of different heights and shapes, and on different layers, can be used to more closely represent the placement area required by a component. Tip If you select the Show 3D Effects option in the User Preferences dialog box (accessed by choosing User Preferences from the Options menu), and have assigned a height for a place outline, Layout displays a three-dimensional image representing the component's height, and indicates the height on the image.

An insertion outline is optional, and is used by Layout to provide clearance for auto-insertion machines.

**Note** An insertion outline can overlap another insertion outline, but a place outline cannot overlap another place outline.

#### To check board, place, and insertion outlines

- 1 Choose the spreadsheet toolbar button, then choose Obstacles. The Obstacles spreadsheet displays.

- 2 Review the Obstacle Type column in the spreadsheet to check that the board, place, and insertion outlines have the correct width and height, and that they are on the correct layer (for example, the board outline must be on the global layer).

- 3 Close the Obstacles spreadsheet so that you can view the board outline in the design window. If there are "cutouts" in the board outline where no components should be placed, you need to create zero-height keepouts inside the cutouts, to ensure that no components are placed in these areas.

For information on creating height keepouts, see *Creating height or group keepins and keepouts* on page 44 . For information on creating board outlines, see Chapter 3, *Setting up board parameters*.

## Checking the place grid

The place grid affects the spacing used for component placement. Before placing components, check the setting for the place grid in the System Settings dialog box.

The default placement grid is 100 mils, with which you can use routing grids of 25 mils, 20 mils,  $12^{1/2}$  mils, 10 mils,  $8^{1/3}$  mils,  $6^{1/4}$  mils, or 5 mils (because 100 mils is a multiple of these values).

The standard metric placement grids are 2 mm, 1 mm, and 0.5 mm.

If you use a 50 mils or 25 mils placement grid, you can use routing grids of 25 mils,  $12^{1/2}$  mils, 10 mils,  $8^{1/3}$  mils, or  $6^{1/4}$  mils.

#### To check the place grid setting

- 1 From the Options menu, choose System Settings. The System Settings dialog box displays.

- 2 Check the value in the Place grid text box, change it if necessary, then choose the OK button.

## Checking mirror layers and library layers

You can check which layers are set up to have their obstacles, padstacks, and text mirrored to another layer during component placement, and change the settings, if necessary. For example, all of the TOP layer components can be automatically mirrored to the BOTTOM layer, and vice versa.

Typically, all inner layers of a design (INNER1, INNER2, and so on) correspond to the INNER library name, and all plane layers of a design (POWER, GROUND) correspond to the PLANE library name. All other layers typically have a one-to-one correspondence; for example, the BOTTOM layer in the design corresponds to the BOTTOM library name.

To check the mirror layer and library layer settings

- 1 Choose the spreadsheet toolbar button, then choose Layers. The Layers spreadsheet displays.

- 2 Check the settings in the Mirror Layer column against the settings in the Layer Name column, to ensure that the layers are set to mirror to their opposite layers.

- 3 Double-click on each layer to bring up the Edit Layer dialog box, check that the Layer LibName is set appropriately, then press ESC to close the dialog box.

## Weighting and color-coding nets

Layout places a higher priority on keeping higher-weighted nets and their components together during placement. In Layout, nets are weighted on a linear scale from 0 to 100.

#### To weight and highlight nets

- 1 Choose the spreadsheet toolbar button, then choose Nets. The Nets spreadsheet displays.

- 2 Double-click in the Net Name cell that corresponds to a net whose weight you want to change, or that you want to highlight. The Edit Net dialog box displays.

- 3 To change the weight for a net, type in a new weight in the Weight text box, then choose the OK button. *or*

Use the scroll bar at the left of the text box to change the number, then choose the OK button. The new number shows in the Weight column of the spreadsheet.

- 4 To highlight a net, select the Highlight option in the Edit Net dialog box, then choose the OK button. The net shows in the highlight color.

- **Tip** To assign a color to a net other than the highlight color, click in the Color cell in the Nets spreadsheet, choose Change Color from the pop-up menu, then select a color from the color palette displayed.

#### To color-code a net

- 1 In the Nets spreadsheet, select the net(s) to which you want to assign a color.

- 2 From the pop-up menu, choose Change Color, then select a color from the palette that displays.

For information on setting net properties, see *Chapter 4, Setting up the board* in the *OrCAD Layout User's Guide.*

## Checking gate and pin information

A package is the electronic gate and pin information associated with a component (as opposed to a footprint, which is the information regarding the physical characteristics of a component). The information in the Packages spreadsheet is used to determine whether you can swap gates between identical components or only within a component, and how the gates are arranged within a part.

#### To check gate and pin information

- 1 Choose the spreadsheet toolbar button, then choose Packages. The Packages spreadsheet displays.

- 2 Verify that the following information in the spreadsheet is correct, then close the spreadsheet.

**Package Name** A text string that designates the name of the electrical package.

**Gate Name** Usually an alpha character that designates which gate each pin belongs to. Each gate in a package must have a unique gate name, and all of the pins in the same gate must share the same gate name.

**Pin Name** Identifies each pin in terms of its electrical characteristics (INA, INB, and so on) so that Layout can swap gates correctly. Each pin within a gate must have a unique identifier. For swappable gates, corresponding pins must have identical pin names.

**Gate Group** An integer used to determine which gates can be swapped. Any gates that are assigned to the same Gate Group are swappable. Gate Group 0 is a special case that represents a non-swappable gate.

**Pin Group** An integer used to determine which pins can be swapped. Any pins that are assigned to the same Pin Group are swappable. Pin Group 0 is a special case that represents a non-swappable pin.

**Pin Type** Usually set to None for standard TTL-type pins, which indicates that the pin is not part of an ECL net, and is not a source, a terminator, or a load. You can assign a Pin Type of None, Source, Terminator, or Load.

## Securing preplaced components on the board

If your design has components or footprints that were placed at the schematic level or as part of the template, you should ensure that they were placed properly before you begin placing additional components. Preplaced components may include connectors, mounting holes, memory arrays, predefined circuits, alignment targets, and components that must be placed in specific locations due to mechanical or temperature restrictions.

Once you are satisfied that the preplaced components are properly placed, you must affix them to the board using the Fix or Lock commands. Otherwise, they may be moved inadvertently when you are placing other components.

The Lock command is temporary; you can easily override the command. However, the Fix command must be disabled in the Edit Component dialog box. The Fix command is intended for parts like connectors and mounting holes that need to be placed permanently in specific locations.

#### To lock components on the board

- 1 Choose the component toolbar button.

- 2 To select all of the preplaced components, hold the left mouse button down while you drag the mouse, drawing a rectangle around the components. Release the left mouse button. Each selected component is highlighted.

- To *temporarily* lock components in a location, choose Lock from the pop-up menu.

*or* To *permanently* fix components in a location, choose Fix from the pop-up menu.

#### To override the Lock command

- Select a few locked components. A dialog box asking "One or more components locked. Override?" displays.

- 2 Choose the OK button. The components are unlocked.

#### To override the Fix command

- 1 Choose the spreadsheet toolbar button, then choose Components. The Components spreadsheet displays.

- 2 Double-click on the row for the component that you want to move. The Edit Component dialog box displays.

- **3** In the Component flags group box, deselect the Fixed option, then choose the OK button.

## Creating height or group keepins and keepouts

You can restrict component placement based on physical constraints using the Comp height keepin or Comp height keepout obstacle types. A height keepin contains all components at or above a specified height, while a height keepout excludes all components at or above a specified height. You can also restrict placement based on group number (assigned in the schematic) using the Comp group keepin or Comp group keepout obstacle types. A group keepin contains all the components in a specified group, while a group keepout excludes all the components in a specified group.

#### To create keepins and keepouts

- 1 Choose the obstacle toolbar button.

- 2 From the pop-up menu, choose New.

- **3** Draw a rectangle that defines the desired keepin or keepout area.

- 4 Double-click on the rectangle. The Edit Obstacle dialog box displays.

- 5 In the Obstacle Type drop-down list, select Comp height keepin or Comp height keepout. In the Height text box, enter a number corresponding to the height of the components you want to include or exclude and choose the OK button.

or In the Obstacle Type drop-down list, select Comp group keepin or Comp group keepout. In the Group text box, enter a number corresponding to the group number of the components you want to include or exclude, then choose the OK button.

- 6 From the pop-up menu, choose Finish. If you created a component height restriction, the rectangle displays the height number and the words "Comp keepin" or "Comp keepout." If you created a component group restriction, the rectangle displays the group number and the words "Group *number* keepin" or "Group *number* keepout."

- Tip If your keepins and keepouts don't display any identifying text (as described in step 6), you may have to enable the Show 3D Effects option. To do so, choose User Preferences from the Options menu. In the User Preferences dialog box, select the Show 3D Effects option, then choose the OK button.

## Loading a placement strategy file

Strategy files set up your display (so you can see what you need to see during component placement) by highlighting appropriate elements such as place outlines, electrical connections, and reference designators, and making irrelevant elements (such as plane layers) invisible. OrCAD recommends loading the strategy file PLSTD.SF before performing manual placement.

#### To load a placement strategy file

- 1 From the File menu, choose Load. The Load File dialog box displays.

- 2 If necessary, change Files of type to Strategy.

- **3** Select PLSTD.SF from the list and choose the Open button.

## Disabling the power and ground nets

If the power and ground nets are not critical to placement, disable routing for all nets attached to plane layers. This significantly improves system performance during placement, as these (typically) large nets often have no bearing on placement.

To disable routing for nets attached to plane layers

- 1 Choose the spreadsheet toolbar button, then choose Nets. The Nets spreadsheet displays.

- **2** Using the CTRL key, select the nets that are attached to plane layers (usually, GND and VCC).

- **3** From the pop-up menu, choose Enable<->Disable. In the Nets spreadsheet, the Routing Enabled column for the nets changes to No.

# Placing components manually

There are several commands available in Layout to assist you in manually placing components on a board. You can place components one at a time or in groups.

Use the Queue For Placement command to make a component or group of components available for placement based on a set of criteria (reference designator, footprint name, or first letters with wildcards), then place the components individually using the Select Next command.

#### To place components individually

- 1 Choose the component toolbar button.

- 2 From the pop-up menu, choose Queue For Placement. The Component Selection Criteria dialog box displays.

- Note The Queue For Placement command and the Select Any command display the same Component Selection Criteria dialog box, but the commands work differently. The Queue For Placement command makes certain components available for placement in conjunction with using the Select Next command. The Select Any command, on the other hand, actually selects specified components or groups for placement and attaches them to your cursor.

- 3 Enter the reference designator (or other criteria) of the component that you want to place in the appropriate text box and choose the OK button. (Choose the dialog box's Help button for information on the options in the dialog box.)

- 4 From the Edit menu, choose Select Next. The component snaps to the cursor. If you selected a group (such as all components beginning with the letter *U*), then the component with the greatest number of connections that meets the specification snaps to the cursor.

- 5 Drag the component to the desired location and click the left mouse button to place it.

For information on matrix placement, moving components, and editing components, see *Chapter 7*, *Placing and editing components* in the *OrCAD Layout User's Guide*.

**Tip** You can specify more than one component using wildcards: use an asterisk (\*) as a substitute for multiple characters and a question mark (?) as a substitute for a single character. For example, if you enter  $U^*$ , you will select all components with reference designators beginning with the letter U.

## Selecting the next components for placement

Use the Place command on the pop-up menu to display a dialog box that lists the components yet to be placed. If you made components available for placement according to certain criteria (using the Component Selection Criteria dialog box), Layout displays only the components that remain to be placed that meet those criteria. From this list, you can select the next component that you want to place.

The default selection that displays in the dialog box is the one that Layout would automatically choose if you had used the Select Next command. You can accept the default, or enter a new choice.

To select the next component for placement using Select Next

- 1 Choose the component toolbar button.

- 2 From the pop-up menu, choose Place. The Select Next dialog box displays.

- **3** Select a component for placement, then choose the OK button.

### Placing component groups

You can assign functionally related components to groups at the schematic level. When you specify the group number (as assigned in the schematic) in the Component Selection Criteria dialog box, the components assigned to the group snap to the cursor for placement.

#### To place a component group

- 1 Choose the component toolbar button.

- 2 From the pop-up menu, choose Select Any. The Component Selection Criteria dialog box displays.

- 3 Enter the group number, as assigned at the schematic level, in the Group Number text box and choose the OK button. The group of components snaps to the cursor.

- 4 Click the left mouse button to place the components on the board.

## Minimizing connections to optimize placement

Use the Minimize Connections command to evaluate the connections within a net and find the shortest route for the net (ratsnest) based on the placement of the pins or components on the board. When nothing is selected, Minimize Connections is a global command; it affects the entire board each time you apply it. However, if you have selected one or more components, Minimize Connections only affects the nets attached to the selected components. You can also select just a single net and minimize the connection length on that net only.

#### To use the Minimize Connections command

- 1 Choose the component toolbar button.

- 2 If desired, select the appropriate component(s) or net(s).

- **3** From the pop-up menu, choose Minimize Connections.

# **Checking placement**

You should check the placement of a board using Placement Spacing Violations, the density graph, and the placement information in the Statistics spreadsheet. For information on how to use the error tool to get more information about reported errors, see Chapter 6, *Finishing the board*.

## **Using Placement Spacing Violations**

Before you route the board, you should run Placement Spacing Violations, which looks for component-to-component spacing violations and other placement errors, such as components that violate height

restrictions, insertion outlines, or grid restrictions.

Tip Placement Spacing Violations uses component outlines to determine whether there is a spacing violation. Therefore, component outlines should encompass the entire area of the IC or discrete component, including such objects as pinout patterns and sockets.

Any problem found by Placement Spacing Violations is marked with a circle. You can find out the nature of the problem by choosing the query toolbar button, which brings up the query window. Then, when you choose the error toolbar button and select the error, the information about the error displays in the query window.

#### To check placement spacing violations

- 1 From the Auto menu, choose Design Rule Check. The Check Design Rules dialog box displays.

- 2 Choose the Clear All button.

- 3 Select the Placement Spacing Violations option, then choose the OK button. Layout checks the board for component placement violations and marks any errors with circles.

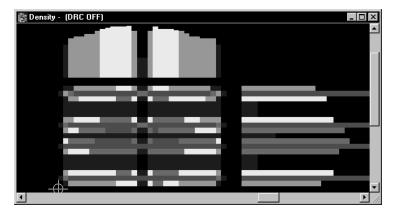

## Using the density graph

The density graph displays a graphical representation of the connection density of your board. Using colors ranging from blue and green (acceptable density) to pink and red (very dense), the density graph represents the degree of difficulty that will be faced in routing the board.

The density graph analyzes all routing layers, routed tracks, widths of tracks, spacing rules, DRC settings, and connections to calculate the available routing channels. It shows the crossing count at each location of the board in relation to how much of each cell is being filled by a pad, track, or connection.

There are two kinds of data shown on the density graph: the *board density* at each location (the number of pads and connections in a given area of the board), and the *track density* (the track density in each channel), shown as bar graphs at the top and right.

#### To open the density graph

- 1 From the View menu, choose Density Graph. The density graph window displays.

- 2 To return to the design window, choose Design from the View menu.

**Note** A small amount of red in the density graph is acceptable, but you should attempt to keep the percentage of red below 25%, because a board that is more than 25% red is likely to encounter serious routing difficulties.

## Viewing placement statistics

When you finish placing components on the board, you can view the component placement statistics in the Statistics spreadsheet. The spreadsheet shows the percentage and number of components placed, how many were placed off the board, how many were unplaced, and how many were placed in clusters.

#### To view placement statistics

- 1 Choose the spreadsheet toolbar button, then choose Statistics. The Statistics spreadsheet displays.

- 2 Scroll until you find the % Placed row, which is the beginning of the placement data.

- **3** Close the spreadsheet when you are finished viewing the statistics.

# **Routing critical nets**

After you have placed the components, you can route the board to form the electrical connections between the components. This chapter explains how to route *critical nets* manually. Critical nets are those that must meet some requirement other than the default settings, such as length.

## **Push-and-shove routing**

Layout's autorouter uses *push-and-shove* routing, which minimizes vias and allows extremely dense autorouting, and *interactive* routing, which allows you to use Layout's automatic routing capabilities without sacrificing routing control.

Wherever Layout's autorouter finds the optimum space in which to place a track, it checks to see if it is possible to "shove" any existing tracks or vias out of the way to get the track in. If that is not possible, the autorouter checks beyond any blocking pads to see if it can jump over them to clear a path.

Layout's autorouter also checks to see if there are obstructing tracks that can be cleared (or rerouted) without deleting anything. If that is not possible, the autorouter looks for the next best location for the track. However, if a path can be cleared by any of Layout's algorithms, Layout clears it, then goes on to the next connection.

# Interactive routing

Layout has an interactive routing feature that allows you to direct routing wherever necessary, while still having access to Layout's autorouting algorithms.

If you have purchased Layout or Layout Plus, you can use the autorouter and enhanced manual routing commands to route the board, then use the manual routing commands described in this chapter to optimize routing.

For information specific to autorouting and enhanced manual routing, see the OrCAD Layout Autorouter User's Guide.

# Before you begin routing

You probably performed the following tasks when you set up the board and placed components. If not, you need to do so to prepare the board for routing.

- Designate appropriate layers as plane layers or routing layers

- Define vias

- Set or verify net properties

- Run Placement Spacing Violations and correct any spacing violations

After you have completed the above items, you are ready to begin the routing process. The steps in the manual routing process are:

- Check the board outline, via definitions, and routing and via grids

- Load a routing strategy file

- Route power and ground

- Fan out SMDs and verify connections to power and ground

- Route the remaining signals using the manual routing tools

- Optimize routing using the manual routing commands

- Check for route spacing violations and check routing statistics

For information on designating layers and defining vias, see Chapter 3, *Setting up board parameters*. For information on setting or verifying net properties, see *Chapter 4, Setting up the board* in the *OrCAD Layout User's Guide*. For information on running Placement Spacing Violations, see Chapter 4, *Placing components*.

For information on optimizing routing using manual routing commands, see *Chapter 8, Routing the board* in the *OrCAD Layout User's Guide.*

## Routing the board manually

When you view the board before you've done any routing, you'll see that the parts have many fine lines running between them. These lines are known as a *ratsnest*. A ratsnest represents the connections that need to be routed to form the necessary tracks on the board. A connection is an electrical path between two pins: a ratsnest represents an unrouted connection, while a track represents a routed connection.

Tip Yellow triangles in a ratsnest indicate unrouted, zero-length connections (connections that lead directly from a pad on the top layer to a pad on the bottom layer without traveling in the X or Y direction).

# Checking the board outline, via definitions, and routing and via grids

Before you route, you need to check the settings for the board outline, vias, routing grid, and via grid.

- Verify that the board outline has a desirable amount of internal clearance, that there is only one board outline, and that it is on the global layer.

- Inspect the vias in the Padstacks spreadsheet to make sure that they are the right size and on the correct layers.

- Verify that the routing grid and via grid match for the placement of tracks.

For information on creating and editing a board outline, defining vias, and setting the routing and via grids, see Chapter 3, *Setting up board parameters*.

## Loading a routing strategy file

A routing strategy file determines which default routing layers to use, when to use vias, which direction the track should travel, which colors to use for routes, and the size of the active routing window. There are many routing strategy files provided with Layout, among which are files for two-layer, four-layer, six-layer, and eight-layer boards. Load the routing strategy file that is most suitable for your board.

**Note** For a complete list of the routing strategy files provided with Layout, see Strategy files in Appendix A, Understanding the files used with Layout in the OrCAD Layout User's Guide.